全部分类

文章

视频

问答

最新发布

最新评论

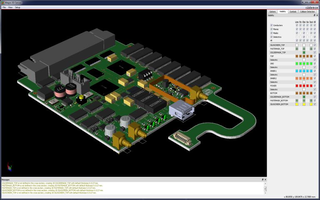

微电子及集成电路技术发展日新月异,离不开EDA电子电路仿真软件的支持。每天不知有多少电路设计及验证者,使用着各种电路仿真软件工具。今天我们聊聊常用的Cadence软件的优缺点。 Cadence 公司是老牌的EDA工具提供商,采用Cadence的软件、硬件和半导体IP,用户能更快速向市场交付产品。Cadence公司创新的"系统设计实现" (SDE)战略,将帮助客户开发出更具差异化的产品——小到芯片大

热榜

1月1年全部

文章

视频

问答

1月1年总榜

项目客服

培训客服

平台客服

顶部